# Gallium Nitride E-mode HEMT GS650EDA165A: 165 m $\Omega$ , 650V

# Description

Gallium Nitride High-Electron-Mobility Transistors (HEMTs) have shown outstanding results in high power applications. The large bandgap results in a high breakdown field, allowing for high operating voltages. Its inherent two-dimensional electron gas (2-DEG) at the AlGaN/GaN interface yields a high electron sheet charge density and mobility, significantly reducing resistive losses in power transistors. Additionally, due to the low gate charge and reverse recovery charge, the switching losses are reduced and switching speeds increased compared to traditional silicon power devices. The p-GaN gate is implemented to ensure the desired enhancement mode (normally-off) operation and improved slew rates.

The GS650EDA165A can be delivered as separate dice in waffle pack or packaged in a DFN 8x8 or DFN 5x6 with exposed paddle allowing an excellent thermal contact.

#### **Features**

- 650V enhancement mode power transistor

- 850V transient drain-to-source voltage

- RDS,ON = 165 mΩ

- IDS,MAX = 10 A

- Ultra-low FOM

- Simple gate drive requirements: 0 to 6 V

- Transient tolerant gate drive: -20 V / +10 V

- High switching frequency > 1 MHz

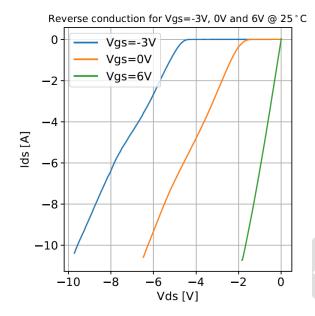

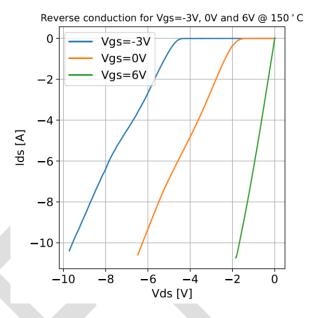

- Reverse conduction capability

- Zero reverse recovery loss

# **Applications**

- Wall wart adapters

- Power Factor Correction

- LED drivers

- Battery Chargers

- Industrial Power Supplies

- Motor drivers

## Outline

## Package

Die

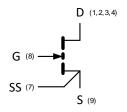

Symbol

# Ordering

The GS650EDA165A is not a product for sale. It is a product sample to demonstrate the capabilities of the Power GaN process.

## Absolute Maximum Ratings (T<sub>J</sub> = 25°C unless otherwise noted)

#### Table 1

| Parameter                                    | Symbol            | Value       | Unit |

|----------------------------------------------|-------------------|-------------|------|

| Operating Junction Temperature               | TJ                | -55 to +150 | °C   |

| Drain to Source Voltage                      | V <sub>DS</sub>   | 650         | V    |

| Drain to Source Voltage – transient (note 1) | $V_{DS,trans}$    | 850         | V    |

| Gate to Source Voltage                       | V <sub>GS</sub>   | -10 to +7   | V    |

| Gate to Source Voltage – transient (note 1)  | $V_{GS,trans}$    | -20 to + 10 | V    |

| Drain Current – continue                     | I <sub>DS</sub>   | 10          | Α    |

| Pulsed Drain Current (note 2)                | I <sub>DS,P</sub> | 17          | Α    |

- (1) For  $t \le 1 \mu s$

- (2) Pulse width 10  $\mu$ s,  $V_{GS} = 6 \text{ V}$

## Thermal Characteristics QFN 8x8 (Typical Values unless otherwise noted)

Table 2

| Parameter                                      | Symbol                | Value | Unit |

|------------------------------------------------|-----------------------|-------|------|

| Thermal Resistance Junction – to – Case        | R <sub>⊛-JC</sub>     | 1,4   | K/W  |

| Thermal Resistance Junction – to – Ambient (3) | $R_{\Theta	ext{-JA}}$ | 36,5  | K/W  |

| Maximum Solder Temperature                     | $T_{SOLD}$            | 260   | °C   |

(3) JEDEC JESD51

#### Electrical Characteristics (Typical Values @ T<sub>J</sub> = 25°C unless otherwise noted)

Table 3

| Parameter                 | Condition                                          | Symbol             | Min | Тур  | Max | Unit |

|---------------------------|----------------------------------------------------|--------------------|-----|------|-----|------|

| Drain to Source Blocking  | $V_{GS} = 0 \text{ V}, I_{DSS} \le 18 \mu\text{A}$ | V <sub>BDSS</sub>  | 650 |      |     | V    |

| Voltage                   |                                                    |                    |     |      |     |      |

| On Resistance             | $V_{GS} = 6 \text{ V}, I_{DS} = 1 \text{ A}$       | R <sub>DSon</sub>  |     | 165  | 220 | mΩ   |

| Gate Threshold Voltage    | $V_{DS} = V_{GS}, I_{DS} = 1.3 \text{ mA}$         | $V_{Th}$           | 0.9 | 2.0  | 3.0 | V    |

| Gate to Source Current    | $V_{GS} = 6 \text{ V}, V_{DS} = 0 \text{ V}$       | I <sub>GS</sub>    |     | 290  |     | μΑ   |

| Drain to Source Leakage   | $V_{DSS} = 650 \text{ V}, V_{GS} = 0 \text{ V}$    | I <sub>DSS</sub>   |     | 0,7  |     | μΑ   |

| Current                   |                                                    |                    |     |      |     | •    |

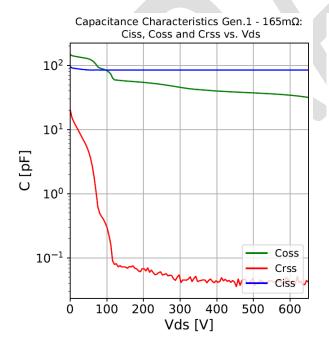

| Input Capacitance         | V <sub>DS</sub> = 400 V                            | C <sub>ISS</sub>   |     | 85   |     | pF   |

| Output Capacitance        | $V_{DS} = 400 \text{ V}$<br>$V_{GS} = 0 \text{ V}$ | Coss               |     | 41   |     | pF   |

| Reverse Transfer          | f = 100 kHz                                        | C <sub>RSS</sub>   |     | 0,04 |     | pF   |

| Capacitance               | 1 = 100 KHZ                                        |                    |     |      |     |      |

| Output Charge             | $V_{DS} = 400 \text{ V}, V_{GS} = 0 \text{ V}$     | Qoss               |     | 27,3 |     | nC   |

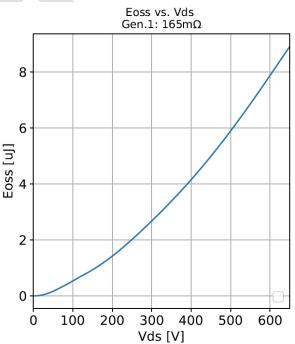

| Output Cap stored energy  | $V_{DS} = 400 \text{ V}$                           | Eoss               |     | 4,2  |     | μJ   |

|                           | $V_{GS} = 0 \text{ V, f} = 100 \text{ kHz}$        |                    |     |      |     |      |

| Total Gate Charge         | Vds = 0  to  400  V,                               | Qg                 |     | 2,2  |     | nC   |

|                           | Vgs = 0 to 6 V                                     |                    |     |      |     |      |

| Effective Output          | Vds = 0  to  400  V,                               | Co <sub>(er)</sub> |     | 52,5 |     | pF   |

| Capacitance, Energy       | Vgs = 0 V                                          |                    |     |      |     |      |

| related                   |                                                    |                    |     |      |     |      |

| Effective Output          | Vds = 0  to  400  V,                               | Co <sub>(tr)</sub> |     | 68,2 |     | pF   |

| Capacitance, Time related | Vgs = 0 V                                          |                    |     |      |     |      |

**Note**: Figures are based on a linear scaling of the 120 m $\Omega$  transistor

Rev 11032024 © 2024 Gansic 2

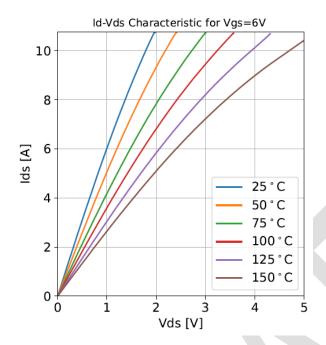

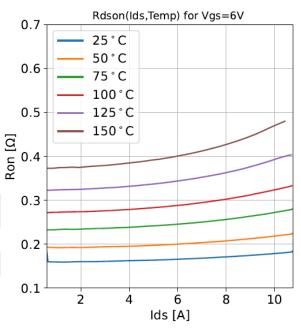

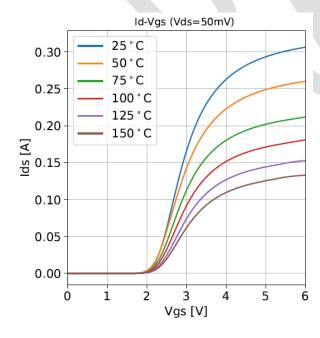

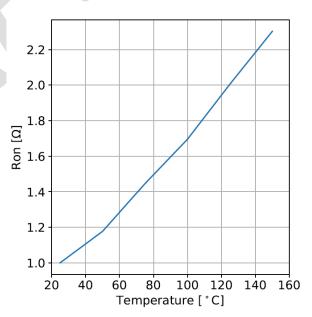

## Electrical Graphs (1/2)

Rev 11032024 © 2024 Gansic 3

## Electrical Graphs (2/2)

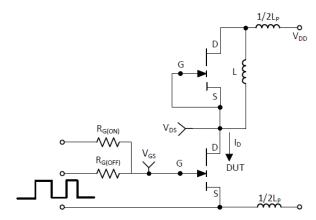

## **Test Circuits**

Fig 13: Switching Test Circuit

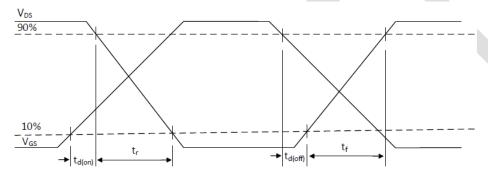

Fig 14: Switching Time Waveforms

## Package Information

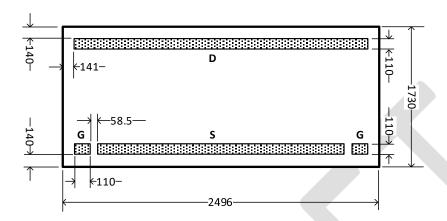

#### Bare Die

Dimensions of the pads in  $\mu m$  refer to the passivation and polyimide opening. Drawing is not to scale.

## Marking

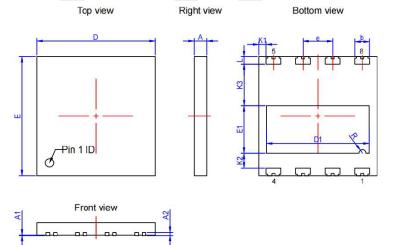

#### DFN 8x8

|                 | SYMBOL | MIN      | NOM  | MAX  |  |

|-----------------|--------|----------|------|------|--|

| TOTAL THICKNESS | Α      | 0.75     | 0.85 | 0.95 |  |

| STAND OFF       | A1     | 0.00     | 0.03 | 0.05 |  |

| L/F THICKNESS   | A2     | 0.203REF |      |      |  |

| LEAD WIDTH      | Ь      | 0.95     | 1.00 | 1.05 |  |

| BODY SIZE X     | D      | 7.90     | 8.00 | 8.10 |  |

| EP SIZE X       | D1     | 6.84     | 6.94 | 7.04 |  |

| BODY SIZE Y     | E      | 7.90     | 8.00 | 8.10 |  |

| EP SIZE Y       | E1     | 3.10     | 3.20 | 3.30 |  |

| LEAD PITCH      | е      | 2.00BSC  |      |      |  |

| SPACING         | K1     | 0.40     | 0.50 | 0.60 |  |

| SPACING         | K2     | 0.90     | 1.00 | 1.10 |  |

| SPACING         | K3     | 2.70     | 2.80 | 2.90 |  |

| LEAD LENGTH     | L      | 0.40     | 0.50 | 0.60 |  |

| RADIUS          | R      | 0.15     | 0.25 | 0.35 |  |

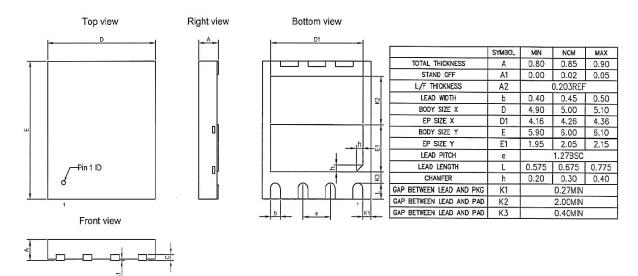

#### DFN 5x6

#### Disclaimer

This Product Sample is not a finished product and is not available for sale to consumers. The Product Sample is only intended for research, development, demonstration, and evaluation purposes and will only be used in laboratory/development areas by persons with an engineering/technical training and familiar with the risks associated with handling electrical/mechanical components, systems and subsystems. These persons assume full responsibility/liability for proper and safe handling of the Product Sample. Any other use, resale or redistribution of the Product Sample for any other purpose is strictly prohibited.